Transistor Evolution: ຈາກ Planar ເຖິງ CFET, ການປະສົມປະສານ 3D ກໍານົດຄວາມຄືບຫນ້າຂອງ Semiconductor

ສໍາລັບຫຼາຍກວ່າເຄິ່ງຫນຶ່ງສະຕະວັດ, ອຸດສາຫະກໍາ semiconductor ເຕີບໂຕໂດຍປະຕິບັດຕາມກົດລະບຽບງ່າຍໆຫນຶ່ງ: ເຮັດໃຫ້ transistors ຂະຫນາດນ້ອຍລົງ.ການຫົດຕົວຂະໜາດຄຸນສົມບັດໃຫ້ປະສິດທິພາບສູງກວ່າ, ພະລັງງານຕໍ່າກວ່າ, ແລະຄ່າໃຊ້ຈ່າຍຕໍ່ transistor ຕໍ່າກວ່າ.ແຕ່ມື້ນີ້, ເສັ້ນທາງນີ້ໄດ້ບັນລຸຂອບເຂດຈໍາກັດທາງດ້ານຮ່າງກາຍແລະເສດຖະກິດ.ຍຸກຂອງການຂະຫຍາຍຕົວທີ່ບໍລິສຸດແມ່ນຫມົດ, ແລະຍຸກໃຫມ່ຂອງ ນະວັດຕະກໍາໂຄງສ້າງ ແລະການເຊື່ອມໂຍງ 3D ໄດ້ເລີ່ມຕົ້ນແລ້ວ.

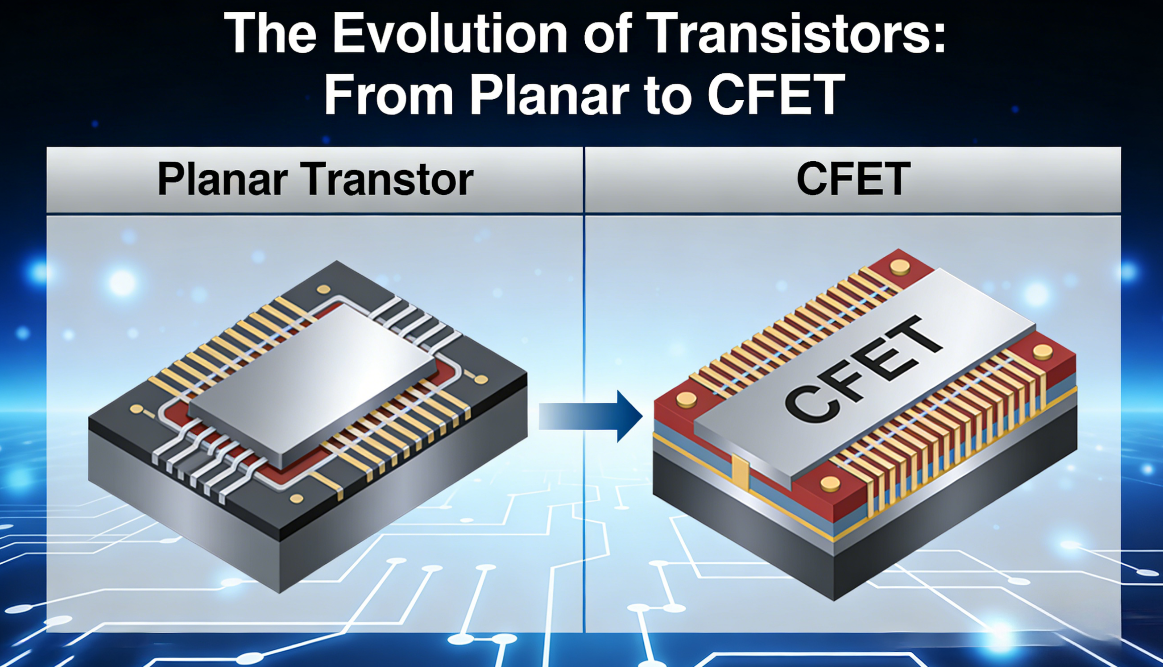

transistor ຕົວຂອງມັນເອງກໍາລັງດໍາເນີນການປະຕິວັດສະຖາປັດຕະຍະກໍາຢ່າງສົມບູນ.ຈາກ planar MOSFET ຫາ FinFET, ຈາກ GAA nanosheet ກັບ CFET stacking, ແຕ່ລະຂັ້ນຕອນສະແດງໃຫ້ເຫັນການປ່ຽນແປງຈາກການຫົດຕົວເປັນ ການກໍ່ສ້າງ transistor ໃນສາມມິຕິ.ນີ້ບໍ່ແມ່ນພຽງແຕ່ການປັບປຸງທີ່ເພີ່ມຂຶ້ນເທົ່ານັ້ນ - ມັນເປັນຄໍານິຍາມໃຫມ່ຂອງຊິບໃຫ້ປະສິດທິພາບ.

ສີ່ລຸ້ນຂອງສະຖາປັດຕະຍະກໍາ Transistor

1. Planar Transistor (2D ແບບດັ້ງເດີມ)

ໂຄງສ້າງຮາບພຽງແບບຄລາສສິກ, ບ່ອນທີ່ປະຕູຮົ້ວຄວບຄຸມຊ່ອງທາງຈາກຂ້າງເທິງ.ມັນຄອບງໍາຈາກຍຸກທໍາອິດລົງໄປຫາ 40nm ແລະ 28nm.ໃນຂະນະທີ່ຂະຫນາດຫຼຸດລົງຕື່ມອີກ, ການຮົ່ວໄຫຼແລະການຄວບຄຸມໄຟຟ້າສະຖິດໄດ້ກາຍເປັນບັນຫາທີ່ບໍ່ສາມາດແກ້ໄຂໄດ້.

2. FinFET (3D Gate Control)

ຊ່ອງດັ່ງກ່າວກາຍເປັນ “fin” ຕັ້ງ, ມີປະຕູຮົ້ວອ້ອມສາມດ້ານ.ອັນນີ້ຊ່ວຍປັບປຸງການຄວບຄຸມໄຟຟ້າສະຖິດຢ່າງຫຼວງຫຼາຍ, ຫຼຸດຜ່ອນການຮົ່ວໄຫຼ, ແລະເຮັດໃຫ້ການຂະຫຍາຍໄດ້ເຖິງ 7nm, 5nm, ແລະແມ້ກະທັ້ງ 3nm.FinFET ກາຍເປັນພື້ນຖານຂອງຍຸກ chip ທີ່ມີປະສິດທິພາບສູງທີ່ທັນສະໄຫມ.

3. GAA Nanosheet (Gate-All-Around)

ຢູ່ທີ່ 2nm ແລະຕ່ໍາກວ່າ, FinFET ຮອດຂີດຈໍາກັດຂອງມັນ.GAA ແທນທີ່ຄີດ້ວຍ nanowires ຫຼືແຜ່ນແນວນອນ stacked, ອ້ອມຮອບປະຕູຢ່າງເຕັມສ່ວນ.ມັນສະຫນອງການຄວບຄຸມທີ່ດີກວ່າ, ພະລັງງານຕ່ໍາ, ແລະປະຈຸບັນຂັບທີ່ສູງຂຶ້ນ.ໃນປັດຈຸບັນ GAA ແມ່ນໂຄງສ້າງຕົ້ນຕໍສໍາລັບຊິບຊັ້ນ 2nm ໃນທົ່ວ TSMC, Samsung, ແລະ Intel.

4. CFET (FET ເພີ່ມເຕີມ)

ຊາຍແດນຕໍ່ໄປ: stacking NMOS ແລະ PMOS ຕັ້ງ.CFET ບັນຈຸສອງ transistors ເຂົ້າໄປໃນຮ່ອງຮອຍຂອງຫນຶ່ງ, ຫຼຸດຜ່ອນພື້ນທີ່ຢ່າງຫຼວງຫຼາຍແລະປັບປຸງຄວາມຫນາແຫນ້ນ.ມັນແມ່ນການສິ້ນສຸດວິວັດທະນາການອັນສຸດທ້າຍຂອງການປັບຂະ ໜາດ ຂອງ transistor ກ່ອນທີ່ລະບົບ 3D ທີ່ແທ້ຈິງຈະສິ້ນສຸດລົງ.

ເປັນຫຍັງການປັບຂະຫນາດດຽວບໍ່ໄດ້ເຮັດວຽກອີກແລ້ວ

- ຄ່າໃຊ້ຈ່າຍໃນຂະບວນການເພີ່ມຂຶ້ນຢ່າງຫຼວງຫຼາຍໃນແຕ່ລະ node ໃຫມ່

- ການຮົ່ວໄຫຼຂອງ Quantum ແລະຂໍ້ຈໍາກັດທາງດ້ານຮ່າງກາຍເຮັດໃຫ້ຂໍ້ຈໍາກັດແຂງກະດ້າງ

- ຄວາມລ່າຊ້າຂອງການເຊື່ອມຕໍ່ກັນແລະການບໍລິໂພກພະລັງງານເກີນຄວາມໄວຂອງ transistor

- chip monolithic ຂະຫນາດໃຫຍ່ທົນທຸກຈາກຜົນຜະລິດຕ່ໍາແລະຄ່າໃຊ້ຈ່າຍສູງ

ອຸດສາຫະກໍາໄດ້ຮັບຮູ້: ການປະຕິບັດບໍ່ໄດ້ມາຈາກ transistors ຂະຫນາດນ້ອຍກວ່າ.ມັນມາຈາກ ການເຊື່ອມຕໍ່ທີ່ດີກວ່າ, ສະຖາປັດຕະຍະກໍາທີ່ສະຫລາດກວ່າ, ແລະການເຊື່ອມໂຍງແນວຕັ້ງ.

ຍຸກໃໝ່: ສາມຊັ້ນຂອງການປະດິດສ້າງ 3D

ຄວາມຄືບຫນ້າຂອງ semiconductor ໃນປັດຈຸບັນຖືກກໍານົດໂດຍສາມມິຕິຂອງການອອກແບບ 3D:

- 3D Transistor: FinFET, GAA, CFET – ການສ້າງ transistor ໃນແນວຕັ້ງ

- ການຈັດວາງອຸປະກອນ 3D: ຄວາມຈຳກ່ຽວກັບເຫດຜົນ, ການຜູກມັດແບບປະສົມ, ການວາງ SRAM

- ການເຊື່ອມໂຍງລະບົບ 3D: Chiplet, ການຫຸ້ມຫໍ່ 2.5D/3D, ການເຊື່ອມໂຍງແບບ interposer

ຮ່ວມກັນ, ພວກເຂົາເຈົ້າປະກອບເປັນ 3D×3D×3D ຍຸກ: transistor, ອຸປະກອນ, ແລະລະບົບທັງຫມົດກາຍເປັນສາມມິຕິລະດັບ.

DTCO: ຄວາມສາມາດຫຼັກໃໝ່

ໃນຂະນະທີ່ການຂະຫຍາຍຂອບເຂດສິ້ນສຸດລົງ, ເຕັກໂນໂລຊີການອອກແບບ Co-Optimization (DTCO) ກາຍເປັນທີ່ສໍາຄັນ.ມັນຫມາຍຄວາມວ່າການອອກແບບສະຖາປັດຕະຍະກໍາຮ່ວມກັນ, ໂຄງສ້າງຂອງ transistor, ເສັ້ນທາງໂລຫະ, ແລະການຫຸ້ມຫໍ່ຕັ້ງແຕ່ເລີ່ມຕົ້ນ.ບໍລິສັດທີ່ເຂັ້ມແຂງທີ່ສຸດບໍ່ແມ່ນພຽງແຕ່ຜູ້ນໍາຂະບວນການເທົ່ານັ້ນ - ພວກເຂົາແມ່ນຜູ້ປະສົມປະສານລະດັບລະບົບ.

ປະສິດທິພາບສາຍໄຟ, ການຈັດສົ່ງພະລັງງານ, ການອອກແບບຄວາມຮ້ອນ, ແລະຄວາມຫນາແຫນ້ນຂອງແບນວິດໃນປັດຈຸບັນກໍານົດປະສິດທິພາບຜະລິດຕະພັນທີ່ແທ້ຈິງ.

AI ເປັນກໍາລັງຂັບລົດສູງສຸດ

AI ແລະຄອມພິວເຕີ້ທີ່ມີປະສິດທິພາບສູງຕ້ອງການແບນວິດ, ປະສິດທິພາບພະລັງງານ, ແລະຄວາມຫນາແຫນ້ນທີ່ບໍ່ເຄີຍມີມາກ່ອນ.ຄວາມຕ້ອງການເຫຼົ່ານີ້ບໍ່ສາມາດຕອບສະໜອງໄດ້ໂດຍການປັບຂະໜາດແບບດັ້ງເດີມ.ເຂົາເຈົ້າຕ້ອງການ:

- ເຊື່ອມຕໍ່ກັນລະຫວ່າງໜ່ວຍຄວາມຈຳ-ຄອມພີວເຕີ ແບນວິດສູງສູງສຸດ

- ປະສິດທິພາບພະລັງງານທີ່ສຸດຕໍ່ການດໍາເນີນງານ

- ຂະຫນານຂະຫນາດໃຫຍ່ແລະການເຊື່ອມໂຍງທີ່ຫນາແຫນ້ນ

AI ໄດ້ບັງຄັບໃຫ້ອຸດສາຫະກໍາທັງຫມົດປະຖິ້ມການປັບຂະຫນາດທີ່ບໍລິສຸດແລະຮັບເອົາການລວມຕົວແບບ 3D ເຕັມຮູບແບບ.

ສະຫຼຸບ: ອະນາຄົດບໍ່ນ້ອຍກວ່າ, ມັນສູງກວ່າ

ອາຍຸຂອງການຫົດຕົວຂອງ transistors ແມ່ນ fading.ອະນາຄົດຂອງ semiconductors ບໍ່ແມ່ນກ່ຽວກັບການເຮັດໃຫ້ອຸປະກອນຂະຫນາດນ້ອຍລົງ - ມັນແມ່ນກ່ຽວກັບລະບົບການກໍ່ສ້າງ ສູງກວ່າ, ໜາແໜ້ນ, ແລະເຊື່ອມຕໍ່ຢ່າງສະຫຼາດກວ່າ.

ຈາກ Planar ກັບ FinFET ໄປ GAA ເຖິງ CFET, transistor ໄດ້ສໍາເລັດການວິວັດທະນາການຂອງຕົນ.ການສູ້ຮົບຕໍ່ໄປຈະຖືກຕໍ່ສູ້ກັບ ການເຊື່ອມໂຍງ 3D, ການຫຸ້ມຫໍ່ແບບພິເສດ, ແລະການອອກແບບລະດັບລະບົບ.ນີ້ແມ່ນບ່ອນທີ່ທົດສະວັດຕໍ່ໄປຂອງຜູ້ນໍາ semiconductor ຈະຖືກຕັດສິນໃຈ.